Some news about progress done on the Universal Chip Analyzer :

- About the UCA itself (modded Mojo v3 board), I found a reliable source for assembled board and they will be modified soon. All firmware features are now implemented and working correctly. UCA FW v1.00 is close.

- About the iAPX86 UCAS, a first batch has been ordered from Elecrow, but they soldered a wrong component on them (well, 50+ wrong components). So I had to send back the whole batch to China. Unfortunately, the package now seems frozen somewhere in China! Tracking is EW001348809FR if you want to check… If it get lost, I will lose $400 and I’ll have to order another batch. Sad.

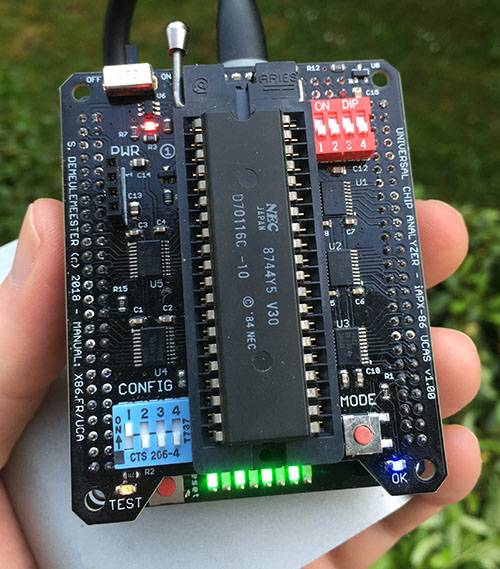

- Anyway, when I got the package from Elecrow, they added two unsoldered PCBs, so I was able to assemble one of them myself to validate the final 1.00 PCB. Good news: everything is working correctly! Signal integrity is much better than on ES/QS, up to 50 MHz, and all hardware bugs are solved. VERY good news. I tested quickly the new expansion port (dedicated for future uses) and it also works as expected.

|

|

- I’m working on a new UCAS Adapter for the Intel 8080. The goal is to use the iAPX86 Shield to test Intel 8080. They requires +5/+12 & -5V, so the Adapter will be an active adapter, but the 8080 is TTL compatible. The design is done and proto PCB will be ordered soon.

- I’m also working on 3 different UCA Shield :

- The MOS/MOT UCAS for Motorola 68xx & MOS 65xx CPUs. There is no real technical difficulties on this one from the tech side.

- The MCS-4/-40 UCAS for Intel 4004 & 4040. LOT of technical challenge here. Interfacing a 45+ years old PMOS CPU that requires -10V/+5V with a modern 3.3V FPGA is quite hard. Especially while using ONLY modern ICs. I’m still working on the schematics right now, messing with comparators, zeners and transistors. The HDL code will not be easy, but I have some ideas.

- A new “Universal PGA Shield” (UPGA). I finally decided to cancel the iAPX-286 Shield that I already showed working on early stages. Why? Because having a 286 UCAS, a 386 UCAS, then a 486 UCAS and another 486 3.3V UCAS, and another 68000/68010/68020/etc. UCAS will be expensive. The UPGA UCAS will support all of them at once, with (quite cheap) interchangeable Sockets. The design have been done, focusing on the fastest 486DX/DX2/DX4. If my design works for them (not proven right now), it will also works with all slower CPUs like 386 or 286. Schematics are done and a nice 4-layer PCB has been designed. It’s a very complex PCB, so I don’t expect the Rev 0.10 to work without massive rework. Fingers crossed!

Now, let me introduce another concept for the UCA : the Xeon ID UCAS! I have big plans for the Universal Chip Analyzer as a truly “Universal” chip analyzer, and this is one of them. Xeons are sometimes hard to identify, especially Engineering Sample (ES are often unmarked, available in various flavor with the same part number, or unknown in databases). Xeon motherboard are also a nightmare to work with, expecting exotic RAM, 2- or 4- CPUs, with BIOS restricted to a few S-Spec. Fortunately, “True” Xeon – like MPs but not the rebranded Desktop CPUs – comes with an embedded “PIROM” chip, used by the motherboard to check their specs without booting the whole CPU. The “Xeon ID UCAS” uses that PIROM to ID the unknown Xeon.

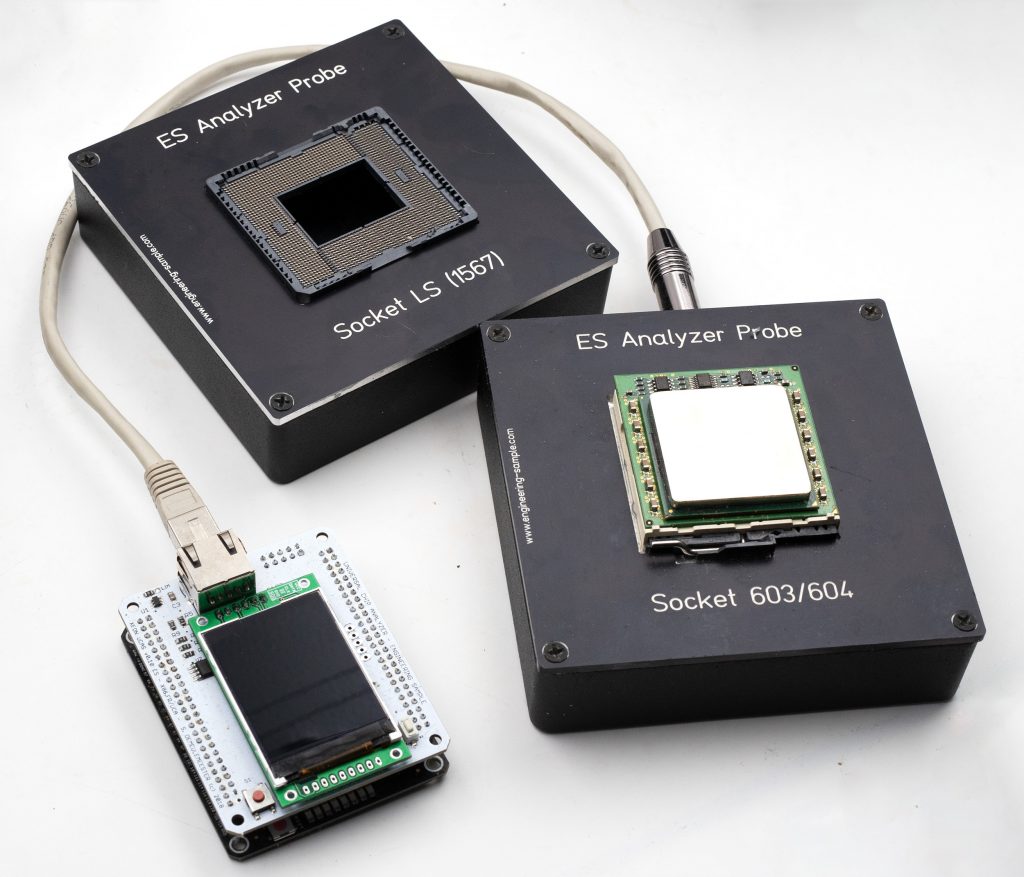

The Shield interfaces with Socket probes to connect with the CPU. Right now, I have a working Socket 603/604 Probe and a LGA1567 Probe, but the UCAS should also work with Pentium II/III Xeon (Slot 2) and up to modern Xeon (LGA2011/3467).

Many information can be grabbed that way. Here is an example with a quite-old Xeon (Gallatin) QF75 ES :

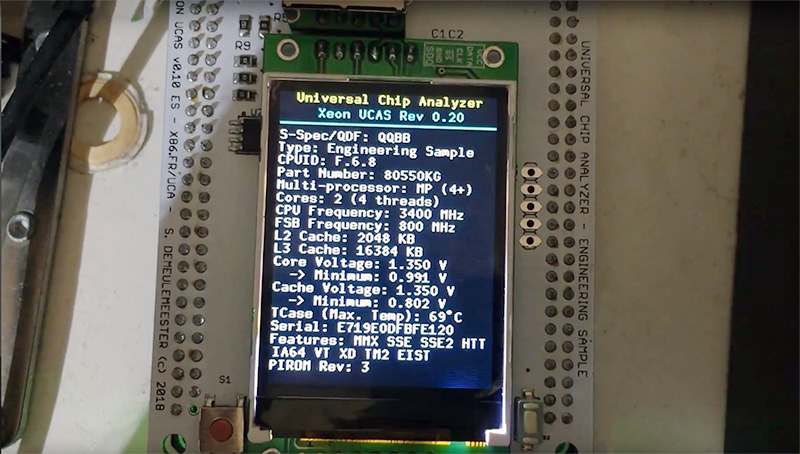

And here with a later Xeon (Tulsa) QQBB ES (Intel Xeon 7140M) :

I also made a small video to let you see how it works:

I also made a small video to let you see how it works:

That’s only a proof-of-concept right now, and the Socket Probe will not be cheap if ever sold, but it looks quite nice 🙂

Stay tuned!