Big milestone! The whole communication between all parts of the UCA (from the MCU synthesized inside the FPGA to the USB port connected on the ATMega) is now working as expected !

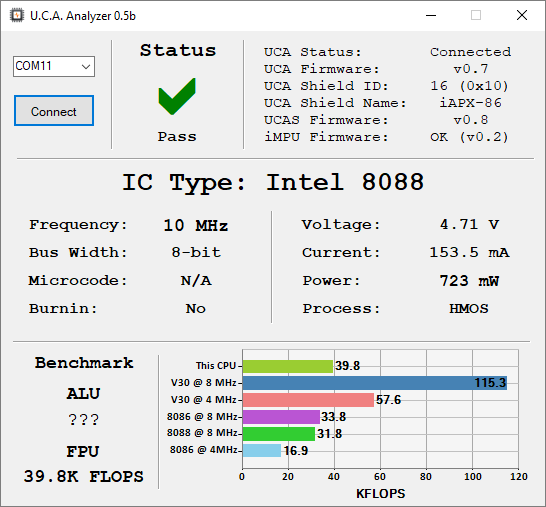

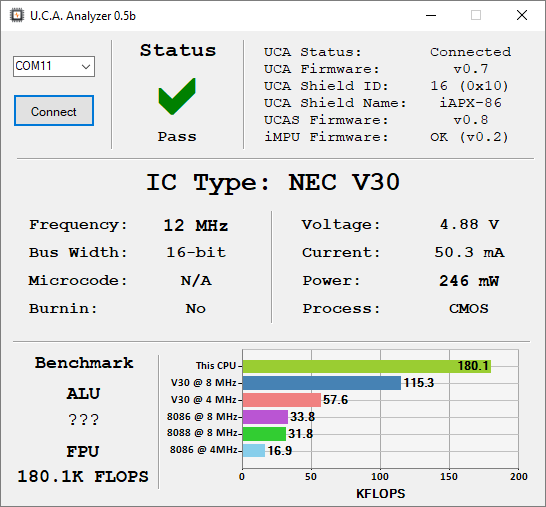

I wrote a simple software in C# this night to show how the advanced features will look like. Top-right, you have the current status of the UCA/UCAS with all the embedded firmware version (yep, there is 3 of them!) . Top-left, the obvious “Connect” Button and the current Status (ranging from “testing” to “Pass” or “Fail” and even “short-circuit”).

In the middle Area, all the feature detected by the UCA : bus width (8088 Vs 8086), Burnin Mode and frequency settings, Microcode (TBD), and also Voltage / Current / Power Drawn by the IC and the corresponding process (CMOS/HMOS/…). I should be able to detect stepping and erratas in hardware for some chips Smile

Finally, in the bottom area, an hardware performance test, 100% handled by the FPGA. Right now, I only wrote the FPU test, but the ALU (Int) test will follow. The absolute value are probably not accurate yet, but the relative KFlops is good. As you can see, the NEC V30 is MUCH faster than a good ol’ 8086 for FPU processing. I will fine tune the benchmark code later, but I’m happy with the progress ^_^

UCA Analyzer in tethered mode testing a Sony CXQ70116P-8 overclocked at 12 MHz

UCA Analyzer in tethered mode testing a P8008-2 overclocked at 10 MHz